## Sistema di acquisizione e distribuzione dati

Per sistema di acquisizione dati, si deve intendere qualsiasi sistema in grado di rilevare e memorizzare grandezze analogiche e/o digitali.

Consiste nell'inviare segnali analogici o digitali ad attuatori come motori, dispositivi riscaldati, relè, teleruttori.

## Sistema di acquisizione e distribuzione dati

E' composto da:

un sistema di misura e contatto con il mondo fisico, in grado di rilevare grandezze fisiche come temperatura velocità

In sistema con un'unità centrale che fornisce i segnali di controllo e acquisizione e di distribuzione e memorizzazioni di controllo e memorizzazioni di controllo e memorizzazioni di controllo e memorizzazione e memorizzazione e memorizzazione. L'unità

Un sottosistema che provvede a generare segnali di uscita che devono comandare motori,relè

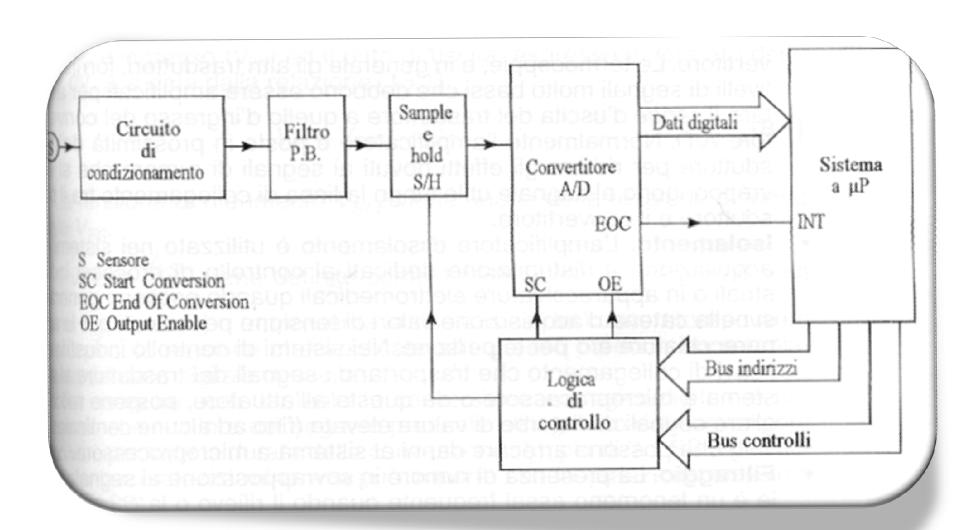

## Architettura generale di acquisizione dati

E' necessario utilizzare circuiti di condizionamento la cui funzione è fondamentale per tutti i blocchi successivi della catena di acquisizione. Infatti,un corretto condizionamento assicura un buon trasferimento dei segnali provenienti dai trasduttori al convertitore ed elimina i disturbi ad esso associati. I circuiti di condizionamento svolgono le seguenti funzioni:

- conversione corrente tensione,

- amplificazione,

- traslazione di livello,

- isolamento,

- filtraggio,

- linearizzazione.

Il blocco S/H è necessario solamente se la variazione del dato è molto veloce, è in grado di memorizzare il valore assunto dal segnale in un determinato istante (fase di sample) e mantenerlo costante all'ingrasso del convertitore, per tutto il tempo impiegato ad effettuare la conversione. Quando la variazione del dato è lenta, si può fare a meno del blocco S/H e il segnale può essere applicato all'ingresso del convertitore A/D.

Il convertitore A/D ha il compito di trasformare il segnale analogico presente al suo ingresso in un segnale digitale a N bit. Ad un convertitore viene applicata una corrente continua particolarmente stabile detta tensione di riferimento (Vref), questa tensione viene anche detta tensione di fondo scala (Vfs). Il rapporto tra Vfs e due volte il numero dei bit rappresenta la risoluzione del convertitore, ovvero la più piccola tensione che applicata all'ingresso produce un cambiamento del dato digitale in uscita.

Il convertitore A/D ha il compito di trasformare il segnale analogico presente al suo ingresso in un segnale digitale a N bit. Ad un convertitore viene applicata una corrente continua particolarmente stabile detta tensione di riferimento (Vref), questa tensione viene anche detta tensione di fondo scala (Vfs). Il rapporto tra Vfs e due volte il numero dei bit rappresenta la risoluzione del convertitore, ovvero la più piccola tensione che applicata all'ingresso produce un cambiamento del dato digitale in uscita.

- •La logica di controllo, costituta normalmente da circuiti di decodifica,o eventualmente da circuiti di temporizzazione,

- •riceve i segnali del bus indirizzi e di controllo del microprocessore e deve generare i segnali di abilitazione per il convertitore e

- •quello per il campionamento e mantenimento del circuito S/H.

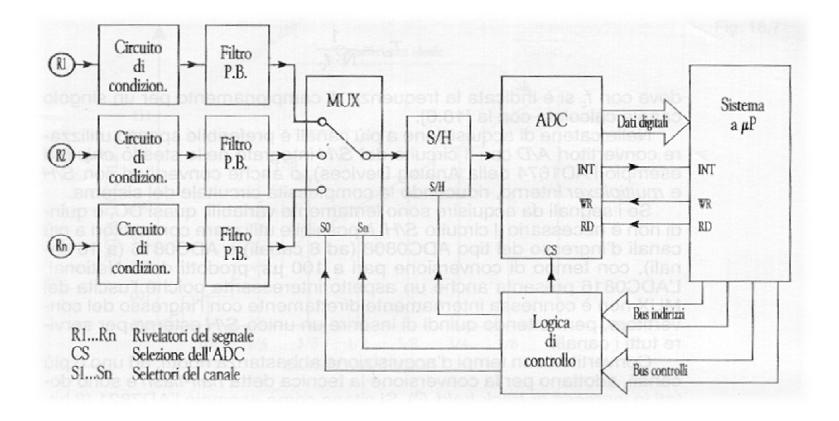

Quando è necessario rilevare più grandezze, il sistema di acquisizione diviene più complesso, composto da catene di acquisizione in parallelo e dipendenti una dalle altre almeno fino al filtro P . B . Nella figura riportata, le frequenze di campionamento non sono elevate . Questa soluzione prevede un unico circuito S/H ed un solo convertitore A/D, la selezione del canale è resa possibile dal multiplexer analogico (MUX), schematizzato con un commutatore elettronico a più ingressi ed una sola uscita.

Un **Mux analogico** è costituito da un certo numero di interruttori elettronici, realizzati o in tecnologia JFET o CMOS o MOSFET che devono presentare elevata resistenza nello stato di off(aperti) e basso in quello di on(chiusi).

Le uscite degli interruttori sono collegate tutte in parallelo e portate verso l'esterno come unica uscita.

Per mezzo di una decodifica interna è possibile chiudere un solo interruttore per volta portando cosi in uscita il solo segnale presente sull'interruttore che viene di volta in volta chiuso.

Spesso il MUX è dotato anche di un ingresso di abilitazione che può disattivare tutti gli ingressi.

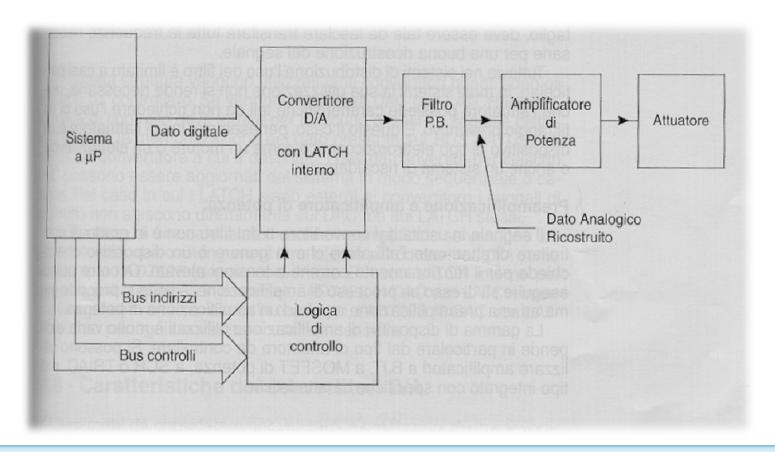

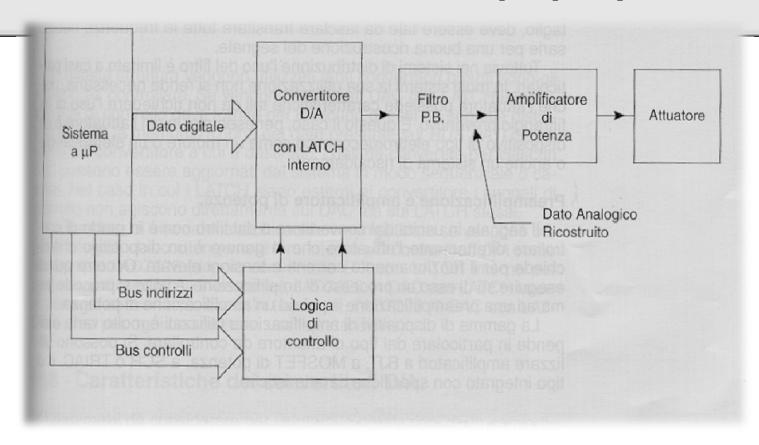

## Sistema di distribuzione dati

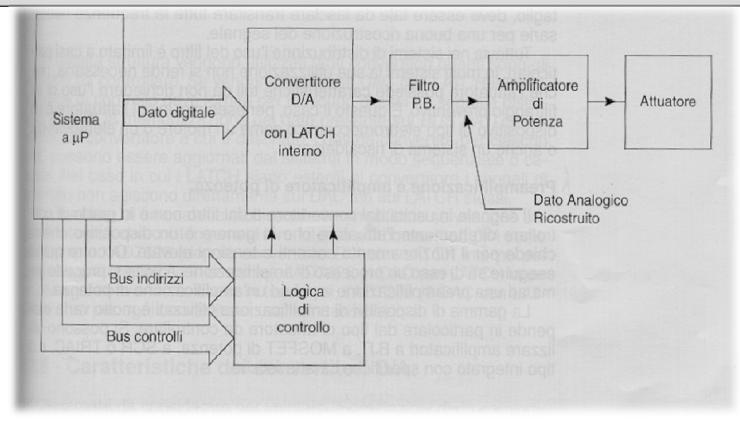

Nella figura riportata si presuppone che si debba agire su un solo attuatore per il controllo di una determinata grandezza fisica(velocità,posizione). In tal coso i dati digitali elaborati dal sistema a microprocessore sono trasformati in dati analogici con un convertitore D/A e , debbono essere stati opportunatamente filtrati se necessario, sono amplificati ed inviati all'attuatore.

Se il convertitore D/A è già dotato di LATCH interni, il dato sul bus dati del sistema a microprocessore è inviato al DAC (convertitore A/D) altrimenti si utilizza una interfaccia d'uscita costituita da flip-flop di tipo D.

La utilizzazione dei LATCH è legata alla necessità di dover mantenere in uscita il dato fornito dalla CPU per tempi più o meno lunghi. Il convertitore effettua la trasformazione digitale - analogica del dato a N bit memorizzato dai LATCH.

Normalmente la logica di controllo è costituita da semplici circuiti di decodifica, e in alcuni casi di temporizzazione, che debbono fornire i segnali di abilitazione per il circuito di LATCH dal convertitore D\A

Tenendo presente che il DAC fornisce in uscita un segnale a gradini e non un vero segnale analogico, è necessario utilizzare un filtro passa-basso per ricostruire la grandezza analogica in modo appropriato, eliminando le componenti di alta frequenza dovute alle discontinuità presenti nel segnale. Il filtro deve possedere una curva di risposta il più possibile piatta all'interno della sua banda passante, e la frequenza di taglio, deve essere tale da lasciare transitare tutte le frequenze necessarie per una buona ricostruzione del segnale.

Il segnale in uscita dal convertitore o dal filtro non è in grado di controllare direttamente l'attuatore che in genere è un dispositivo che richiede per il funzionamento correnti e tensioni elevate. Occorre eseguire su di esso un processo di amplificazione. A volte si procede prima ad una preamplificazione e poi ad un'amplificazione di potenza. La gamma di dispositivi di amplificazione utilizzati è molto varia e dipende in particolare dal tipo di attuatore da controllare. Si possono utilizzare amplificatori a BJT,MOSFET di potenza a SCR o TRIAC, o di tipo integrato con specifiche caratteristiche.

In questa struttura vengono utilizzati tanti convertitori quanti sono gli attuatori da controllare. Se vengono adoperati DAC con LATCH interno,la logica di controllo deve fornire per ciascuno di essi un segnale distinto che abiliti la memorizzazione del dato presente sul BUS DATI del sistema sul convertitore a cui è destinato.I dati da convertire per ciascun DAC possono essere aggiornati dal sistema in modo sequenziale o casuale.Nel caso in cui i LATCH siano esterni al convertitore i segnali di controllo non agiscono direttamente sul DAC ma sui LATCH stessi.LA struttura di una catena a multicanale è semplificata se vengono utilizzati integrati che contengono al loro interno più convertitori D/A.

I convertitori A/De D/A sono realizzati in modo tale da poter essere collegati direttamente con i microprocessori per implementare sistemi di acquisizione e distribuzione dati . Questi dispositivi presentano alcuni pin collegati direttamente con quelli corrispondenti presenti sulla CPU. In una generica catena per l'acquisizione dati analogica il segnale all'uscita del traduttore viene trasformato e filtrato per essere poi inviato al convertitore attraverso il MUX ed il S/H. Nell'analisi della catena di acquisizione, il S/H. il MUX e l'A/D sono dispositivi che debbono essere considerati come generiche periferiche che come tali vanno collegate alla CPU o al BUS del PC. Il convertitore è una periferica di input/output mentre S/H e MUX analogico sono di output.